**Operating Manual**

# Lock-In Amplifier Module Series LIA-MV(D)-200

© 9/2018 Rev. 6

# **Table of Contents**

| 1     | INTRODUCTION                                                       | 4  |

|-------|--------------------------------------------------------------------|----|

| 2     | MODELS OF THE LIA-MV(D)-200 SERIES                                 | 4  |

| 3     | ABSOLUTE MAXIMUM RATINGS                                           | 5  |

| 4     | SPECIFICATIONS                                                     | 5  |

| 5     | STANDARD CONFIGURATION OF THE LOCK-IN AMPLIFIER (FACTORY SETTINGS) | 8  |

| 5.1   | Amplifiers without Optional SOM-1 Module                           | 8  |

| 5.2   | Amplifiers with Optional SOM-1 Module                              | 8  |

| 6     | GETTING READY TO USE THE LIA-MV(D)-200                             | 9  |

| 7     | MANUAL OPERATION                                                   | 9  |

| 7.1   | LED Indications                                                    | 10 |

| 7.2   | Gain and Dynamics                                                  | 10 |

| 7.3   | Adjusting the Phase                                                | 14 |

| 7.3.1 | Phase Shifter Resolution of 8 Bit                                  | 14 |

| 7.3.2 | Phase Shifter Resolution of 7 Bit                                  | 15 |

| 7.4   | 2f-Mode                                                            | 15 |

| 7.5   | Time Constant and Filter Characteristics                           | 16 |

| 7.6   | DIP Switches S1-S4                                                 | 17 |

| 8     | OPERATION WITH CONTROL INTERFACE                                   | 18 |

| 8.1   | Assignment of the SUB-D 25 Pin Socket                              | 18 |

| 8.2   | Overview of all Digitally Controllable Functions                   | 19 |

| 9     | MIXED OPERATION                                                    | 22 |

| 10     | ADVANCED CONFIGURATION OF THE LOCK-IN AMPLIFIER                | 22 |

|--------|----------------------------------------------------------------|----|

| 10.1   | Opening and Closing the Device                                 | 22 |

| 10.2   | Optional Sine-Oscillator-Module SOM-1                          | 23 |

| 10.3   | Modification of the Input Signal Filters                       | 24 |

| 10.4   | Setting the Working Frequency Range (H-Models Only)            | 24 |

| 10.5   | Changing the Assignment of the BNC Sockets                     | 26 |

| 10.5.1 | Options for the Assignment of the BNC Socket "REFERENCE INPUT" | 27 |

| 10.5.2 | Options for the Assignment of the BNC Socket "SIGNAL INPUT"    | 28 |

| 10.5.3 | Options for the Assignment of the "OUTPUT" BNC Sockets         | 29 |

|        |                                                                | 00 |

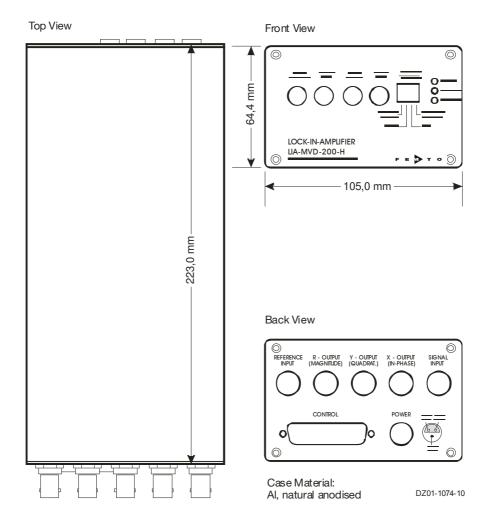

| 11     | DIMENSIONS                                                     | 30 |

| 12     | BLOCK DIAGRAM                                                  | 31 |

# F E T O

# 1 Introduction

Lock-in amplifiers are used to measure weak signals which may be hidden in background noise of much higher amplitude than the actual signal that needs to be measured.

A lock-in amplifier is essentially a frequency and phase sensitive AC-voltmeter which allows detecting a weak signal at a specific frequency and phase which is provided by a reference source.

FEMTO's LIA-MV(D)-200 Series Lock-In Amplifier Modules cover a wide frequency range up to 120 kHz. The input can be configured as voltage or current input and the sensitivity can be varied over a wide range. For adjusting the phase a digital phase shifter is included with a resolution of 1.4°. Further control elements for setting the time-constant, dynamic reserve, 1f/2f mode and the reference signal characteristic are provided as well. All functions can be controlled locally my manual switches or by the digital remote interface with TTL/CMOS control signals. Therefore the device is ideally suited for use as a stand-alone unit or as part of a complex measuring system.

The miniature module LIA-MV-150 with even smaller dimensions and the 19"-board version LIA-BV(D)-150 complete FEMTO's spectrum of lock-in amplifiers for use in scientific or industrial applications.

# 2 Models of the LIA-MV(D)-200 Series

The LIA-MV(D)-200 Series Lock-In Amplifier Modules are complete single phase or dual phase lock-in amplifiers in an robust aluminum housing.

The following models are available:

| LIA-MV-200-L  | - | single phase, working frequency | 5 Hz 10 kHz   |

|---------------|---|---------------------------------|---------------|

| LIA-MV-200-H  | - | single phase, working frequency | 50 Hz 120 kHz |

| LIA-MVD-200-L | - | dual phase, working frequency   | 5 Hz 10 kHz   |

| LIA-MVD-200-H | - | dual phase, working frequency   | 50 Hz 120 kHz |

While single phase units only offer the X signal which is in phase with the reference signal the dual phase models also offer Y (90° phase shifted with respect to the reference signal) and R signals (magnitude, vector sum of X and Y). Please note when using a LIA-MV**D**-200 dual phase lock-in amplifier that due to the square wave mixer used inside the lock in a true phase independent measurement is only possible for a sinusoidal input signal. If your input signal has a different form the R output may still show a moderate phase dependence.

The basic specifications of the four models are similar. Differences or extended specifications are outlined in this manual.

The optionally available Sine-Oscillator Module SOM-1 provides an internal reference signal.

# 3 Absolute Maximum Ratings

| Supply Voltage:          | ±22 V       |

|--------------------------|-------------|

| Signal Input Voltage AC: | $50 V_{PP}$ |

| Reference Input Voltage: | ±15 V       |

| Logic-Inputs:            | –5 +15 V    |

Exceeding the absolute maximum ratings may result in damage to the lock-in amplifier.

# 4 Specifications

#### **Voltage Signal Input**

| Configuration:              | instrumentation amplifier, true-differential                 |

|-----------------------------|--------------------------------------------------------------|

| Voltage Range (Full Scale): | $3 \mu V_{rms}$ to $1  V_{rms}$ (switchable in 1-3-10 steps) |

| Coupling:                   | AC                                                           |

| Gain Drift:                 | < 100 ppm/ K                                                 |

| Input Impedance:            | 1 MΩ    4 pF                                                 |

| Voltage Noise:              | 12 nV/√Hz                                                    |

| Common Mode Rejection Rati  | 0                                                            |

| (CMRR):                     | 110 dB @ 1 kHz, 100 dB @ 10 kHz                              |

|                             |                                                              |

#### **Current Signal Input**

| Configuration:              | transimpedance amplifier, –100 kV/A, (inverting) |

|-----------------------------|--------------------------------------------------|

| Current Range (Full Scale): | 30 pA <sub>rms</sub> to 10 μA <sub>rms</sub>     |

|                             | (switchable in 1-3-10 steps)                     |

| Coupling:                   | DC                                               |

| Current Noise:              | 0.4 pA/√Hz                                       |

| Source Capacitance:         | 10 pF – 500 pF                                   |

|                             |                                                  |

#### **Signal Input Filter**

| Adjustment:                | cut-off frequencies (–3 dB) via internal jumpers |

|----------------------------|--------------------------------------------------|

| Upper-Cut-Off-Frequencies: | 100 Hz / 1 kHz / 10 kHz / 100 kHz / 1 MHz        |

| Lower-Cut-Off-Frequencies: | Model –L: 0.2 Hz / 1 Hz / 10 Hz / 100 Hz / 1 kHz |

|                            | Model –H: 2 Hz / 10 Hz / 100 Hz / 1 kHz / 10 kHz |

| Characteristic:            | 6 dB / Octave                                    |

| Frequency Accuracy:        | ±20 %                                            |

#### **Reference Input**

| Input Voltage Range:                                                   | bipolar: ±100 mV to ±5 V<br>(comparator threshold: 0 V)<br>TTL: –5 V to +10 V<br>(comparator threshold: +2 V) |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Input Impedance:<br>Acquisition Time<br>Slow Setting:<br>Fast Setting: | 1 MΩ    10 pF<br>4 s max.<br>2 s max.                                                                         |

#### Phase

|   | Adjustment Range:<br>Resolution:                                                                       | 0 - 360°, digitally controlled<br>1.4° (8 bit) or 2.8° (7 bit)<br>drift: < 100 ppm / K                                                                                              |

|---|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Accuracy:<br>Orthogonality:                                                                            | > 0.3°<br>< 0.1°                                                                                                                                                                    |

| D | ynamic Reserve                                                                                         |                                                                                                                                                                                     |

|   | Demodulator:                                                                                           | 15 dB @ "ultra-stable" setting<br>35 dB @ "low drift" setting<br>55 dB @ "high dynamic" setting                                                                                     |

|   | Output                                                                                                 |                                                                                                                                                                                     |

|   | Output Channels:                                                                                       | X – in phase<br>Y – quadrature (dual phase models only)<br>R – magnitude (dual phase models only)                                                                                   |

|   | Output Voltage:<br>Output Current:                                                                     | $\pm 10 \text{ V} @ > 2 \text{ k}\Omega \text{ load}$<br>$\pm 5 \text{ mA max.}$                                                                                                    |

|   | Impedance:<br>DC-Drift:                                                                                | 50 $\Omega$ (terminate with load > 10 k $\Omega$ for best results)<br>5 ppm / K @ "ultra-stable"setting<br>50 ppm / K @ "low drift" setting<br>500 ppm / K @ "high dynamic" setting |

|   | Basic Accuracy:                                                                                        | 2 % (X and Y output)<br>for sinusoidal input signal                                                                                                                                 |

|   | Vector-Sum Accuracy:                                                                                   | 4 % (dual phase models only)<br>for sinusoidal input signal                                                                                                                         |

|   | Output Offset Range:                                                                                   | $\pm 100$ % full scale with $\pm 10$ V control voltage                                                                                                                              |

| S | ignal Monitor Output                                                                                   |                                                                                                                                                                                     |

|   | Monitor Gain:<br>Monitor Output Voltage Range:<br>Monitor Output Impedance:<br>Monitor Output Current: |                                                                                                                                                                                     |

|   |                                                                                                        |                                                                                                                                                                                     |

#### **Time Constants**

| Range:                 | model –L: 3 ms to 10 s          |

|------------------------|---------------------------------|

|                        | (switchable in 1-3-10 steps)    |

|                        | model –H: 300 µs to 1 s         |

|                        | (switchable in 1-3-10 steps)    |

| Filter-Characteristic: | 6 dB or 12 dB/octave switchable |

# **Digital Control**

| Control Voltage | high:       | +1.8 V +12 V                                  |

|-----------------|-------------|-----------------------------------------------|

|                 | low:        | –0.8 V +0.8 V                                 |

| Control Current |             | 0 mA @ 0V; 1.5 mA @ +5 V; 4.5 mA @ +12 V typ. |

| Output Voltage  | active:     | +4.5 V typ.                                   |

|                 | non active: | 0 V typ.                                      |

| Output Current:  | 10 mA max.                   |

|------------------|------------------------------|

| LED Indications: | overload, unlocked and power |

#### **Power Supply**

| Supply Voltage: | ±15 VDC min.                               |

|-----------------|--------------------------------------------|

|                 | ±18 VDC max.                               |

| Supply Current: | +120 mA; –60 mA typ. (depends on operating |

|                 | conditions, recommended power supply       |

|                 | capability minimum ±150 mA)                |

# Temperature Range

| Operating: | 0 °C +50 °C    |

|------------|----------------|

| Storage:   | –40 °C +100 °C |

#### **Dimensions and Weight**

| Dimensions: | 105 mm x 223 mm x 64 mm<br>(without BNC sockets) |

|-------------|--------------------------------------------------|

| Weight:     | approx. 1000 g (2.2 lbs)                         |

#### 5 Standard Configuration of the Lock-In Amplifier (Factory Settings)

#### 5.1 Amplifiers without Optional SOM-1 Module

Standard factory settings are as follows:

- The BNC socket "SIGNAL INPUT" is configured as single ended AC coupled voltage input

- The output signal is available as in-phase signal at the BNC terminal "OUTPUT X". In addition the dual phase models LIA-MVD-200 provide quadrature and vector-sum outputs at "OUTPUT Y" and "OUTPUT R", respectively.

- The lower cut-off input signal filter is set to 0.2 Hz for L-models and to 2.0 Hz for H-models. The upper cut-off frequency is set to > 1 MHz for both models.

- The working frequency range for L-models is 5 Hz...10 kHz, 1f-mode and 2f-mode are possible. The phase shifter resolution is 8 bit at 1f-mode and 7 bit at 2f-mode.

The working frequency range for H-models is set to 50 Hz...120 kHz, only 1fmode is supported (DIP switch S2 is without function in this setting). The phase shifter resolution is 7 bit.

- The signal monitor output is not externally available.

- The external reference voltage must be fed to the BNC socket "Reference INPUT"

To change the standard configuration see chapter 9.

#### 5.2 Amplifiers with Optional SOM-1 Module

The lock-in amplifiers can be equipped with the optional SOM-1 reference signal module. The standard configuration is similar to the one described in chapter 5.1 except for the BNC socket "REFERENCE INPUT" which now functions as output socket.

The internal SOM-1 module generates a sine wave reference signal. It is directly connected to the internal lock-in reference input. Factory set to 1 kHz and 1  $V_{\rm rms}$  this reference signal is also available at the BNC terminal "REFERENCE INPUT" for external use.

### 6 Getting Ready to Use the LIA-MV(D)-200

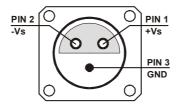

The LIA-MV(D)-200 requires a DC supply voltage of  $\pm$  15 V connected to the 3-Pin LEMO socket on the backside of the amplifier.

We recommend using the PS-15 FEMTO power supply as it is designed for optimum performance of the lock-in amplifier.

Figure 1: 3-Pin-LEMO Socket

The positive and negative supply voltages should be switched on simultaneously.

In order to avoid noise pickup you should use a coaxial cable to connect the signal source or the preamplifier to the lock-in signal input. The factory setting for the input is an AC coupled voltage input configuration. For changing this setting please see chapter 9.

An external reference signal needs to be connected to the BNC socket "REFERENCE INPUT". Please use coaxial cables for the reference signal as well and make sure that the signal is in the correct voltage and frequency range. If you ordered a lock-in amplifier with optional SOM-1 reference oscillator the reference signal is generated internally and can be picked up at the BNC socket labeled "REFERENCE INPUT" for external use in your set-up.

Finally, the signal outputs should be connected using coaxial cables to a voltmeter, analog/digital converter, oscilloscope or similar.

#### 7 Manual Operation

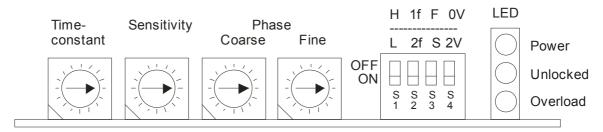

The parameters of the lock-in amplifier are controlled by four hexadecimal switches (0 - F) and four DIP switches on the front panel.

Figure 2: View of the front panel switches

#### 7.1 LED Indications

The LEDs on the front panel provide the status information:

| Power(green)   | power supply on                                                |

|----------------|----------------------------------------------------------------|

| Overload (red) | noise level too high, dynamic reserve not sufficient,          |

|                | incorrect gain range                                           |

| Unlocked (red) | PLL not locked, reference signal not connected or out of range |

#### 7.2 Gain and Dynamics

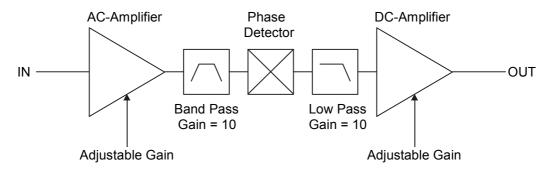

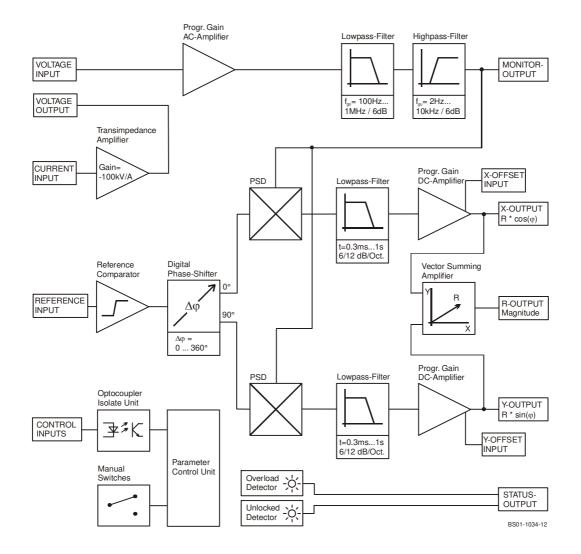

Figure 3: Block diagram

The block diagram shows the path along the involved stages:

- AC-amplifier amplifies the input signal for further processing along the lock-in signal path.

- Input band pass filter with adjustable upper and lower frequency limits useful for eliminating strong noise or perturbation components.

- Phase detector this is the core of the lock-in amplifier which multiplies the input signal (including the noise) with the reference signal. This process is also know as mixing and translates the actual signal at the reference frequency down to DC level.

- Low pass filter with adjustable time constant responsible for eliminating all non-DC components and for smoothing the output.

- DC-amplifier amplifies the smoothed signal to the desired output level.

The gain of the AC-amplifier at the signal input and the gain of the DC-amplifier at the output can be adjusted via the hexadecimal switch "Sensitivity" (settings  $0_{hex}$  to  $F_{hex}$ ) and via the DIP switch S1 "Dynamic Reserve" on the front panel.

A very important parameter is the required dynamic reserve which is the ratio of the largest tolerable noise level to the signal for full scale output. For example, if the lock-in is set to a sensitivity of 10  $\mu$ V for a full scale output a dynamic reserve of 40 dB means that the noise level can go up to 1 mV (= 40 dB equals a factor of 100) without overloading the amplifier. In this setting a 10  $\mu$ V<sub>ms</sub> input signal covered in up to 1 mV noise will result in the full scale output of the lock-in amplifier (10 V DC at the output). Even smaller input signals can be measured in this setting. In our example an input signal of 1  $\mu$ V<sub>ms</sub> will result in an output signal of 1 V DC even if the noise level is still 1 mV at the input.

A certain amount of overall gain can be achieved either by <u>bick AC-amplification and</u> low DC-amplification or by low AC-amplification and high However, the consequences with respect to DC-stability a contrarv and require a careful selection of the settings. Fo (供3种不同的工作模式,以在各种应用中动态保留 LIA-MV(D)-200 lock-in amplifiers offer 3 different modes o best possible compromise between dynamic reserve and 的动态保留至少为55 dB; applications:

- High Dynamic Reserve for small signals with high 1所述,可以通过两种不同的开关设置组合来实现 • reserve in this setting is at least 55 dB; the DC drift

- Low Drift for medium signals with medium noise I 极佳,仅为5 ppm / K; 动态储备为15 dB。 is 35 dB; the DC drift is 50 ppm/K; this mode is ach combinations of switch settings as described in tab

- Ultra-Stable for a very stable output signal; the D 5 ppm/K; the dynamic reserve is 15 dB.

•低漂移-适用于中等噪声水平的中等信号; 态储备为35 dB; 直流漂移为50 ppm / K; 如下表 此模式

DC漂移

The following parameters determine the distribution of the overall gain to the various stages. Table 1 lists these parameters for the 3 different modes of operation:

- い下参数确定总增益在各个阶段的分布。表1列出了 种不同操作模式下的这些参数:・感兴趣信号的输入电 在一部分子型示了在没有过载的情况下 Circumstances of the measurement set-up. The Signal" show the maximum input level for linea い下参数确定总增益在各个阶段的分布。表1列出了 种不同操作模式下的这些参数:・感兴趣信号的输入电 "输入信号"列中的数字显示了在没有过载的情况下 线性锁定的最大输入电平。此最大输入电平将导致1 Signal" show the maximum input level for linea v的满量程输出。 without overload. This maximum input level will the maximum input level wil

- Stability of the output The stability of the lock-in output is mainly dete drift of the DC-amplifier. To optimize the stabili amplification should be kept as low as possible parameters. The temperature drift is thus minin

- Maximum dynamic reserve As outlined above the dynamic reserve is a measure of the lock-in's ability to recover signals that are buried in noise. For measurements with high noise levels or other spectral components which cannot be rejected by the adjustable band pass filter ahead of the phase detector the dynamic reserve should be increased to guarantee that the actual signal can be extracted from the noise components.

We recommend starting with the "Ultra-Stable" mode if high noise is not expected. In this setting the value of the noise signals can be still 6 times (15 dB) higher than the selected sensitivity setting. An adjustment of the phase shifter should be performed to ensure that the output signal reached the maximum possible value.

If despite of a low output signal level the "Overload-LED" is lit the phase detector might be overloaded due to high noise components. In this case switch to the "Low

# FE TO

Drift" or "High Dynamic Reserve" modes to increase the dynamic reserve and to avoid an overload of the phase detector by noise signals. This will result in lower output stability though as the temperature drift increases.

If the "Overload-LED" is on even in the "High Dynamic" mode with the output not yet reaching 10 V an extremely high interfering or noise signal has been picked up and the lock-in amplifier is not able to work properly. In this case check carefully all connections between the lock-in amplifier and the signal source, especially screening and grounding. Additionally a modification or adjustment of the switchable low and high pass filter may cure the problem (see chapter 9 for details).

For the single phase models LIA-MV-200 a phase adjustment is necessary to achieve best performance and to select the optimum sensitivity setting (see the following chapter 7.3). For the dual phase models LIA-MVD-200 a phase adjustment is recommended if the input signal is not of sinusoidal shape as otherwise the square wave mixer used inside the lock-in will not produce optimum results (see also chapter 2).如果不希望出现高噪音,建议从"超稳定"模式开始。

在此设置中,噪声信号的值仍可以比所选灵敏度设置高6倍(15 dB)。应该对移相器进行调整,以确保输出信号达到最大可能值。

如果尽管输出信号电平较低,但"Overload-LED"点亮,则由于高噪声成分,相位检测器可能过载。在这种情况下,请切换到"Low漂移"或"高动态储备"模式,以增加动态储备并避免噪声信号使鉴相器过载。尽管随着温度漂移的增加,这将导致较低的输出稳定性。

如果即使在"高动态"模式下,"过载LED"仍亮着,而输出仍未达到10 V,则说明拾取 了极高的干扰或噪声信号,并且锁相放大器无法正常工作。在这种情况下,请仔细检 查锁定放大器和信号源之间的所有连接,尤其是屏蔽和接地。另外,对可切换的低通 和高通滤波器进行修改或调整可以解决该问题(有关详细信息,请参阅第9章)。

对于单相型号LIA-MV-200,必须进行相位调整才能获得最佳性能并选择最佳灵敏度 设置(请参阅以下第7.3章)。对于双相型号LIA-MVD-200,如果输入信号不是正弦波 形状,则建议进行相位调整,否则锁相器内使用的方波混频器将不会产生最佳效果 (另请参见第2章)。 The following table 1 lists the main parameters of the lock-in amplifier for the 3 different modes of operation and in dependence of the selected sensitivity setting.

| Mode            | Characteristics       | Input Signa<br>Full Scale |         | Total Gain | Gain    |         | Switch Setting   |                  |

|-----------------|-----------------------|---------------------------|---------|------------|---------|---------|------------------|------------------|

|                 |                       | Voltage                   | Current |            | AC-Gain | DC-Gain | Hex Switch       | DIP Switch<br>S1 |

| High<br>Dynamic | Small signal          | 3 µV                      | 30 pA   | 3x10^6     | 300.0   | 100     | F <sub>HEX</sub> | Н                |

| Reserve         | high noise level      | 10 µV                     | 100 pA  | 1x10^6     | 100.0   | 100     | E <sub>HEX</sub> | Н                |

|                 | dynamic reserve 55 dB | 30 µV                     | 300 pA  | 3x10^5     | 30.0    | 100     | D <sub>HEX</sub> | Н                |

|                 | DC-drift 500 ppm/K    | 100 µV                    | 1 nA    | 1x10^5     | 10.0    | 100     | C <sub>HEX</sub> | Н                |

|                 |                       | 300 µV                    | 3 nA    | 3x10^4     | 3.0     | 100     | B <sub>HEX</sub> | Н                |

|                 |                       | 1 mV                      | 10 nA   | 1x10^4     | 1.0     | 100     | A <sub>HEX</sub> | н                |

|                 |                       | 3 mV                      | 30 nA   | 3x10^3     | 0.3     | 100     | 9 <sub>HEX</sub> | Н                |

|                 |                       | 10 mV                     | 100 nA  | 1x10^3     | 0.1     | 100     | 8 <sub>HEX</sub> | Н                |

| Low Drift       | medium signal         | 30 µV                     | 300 pA  | 3x10^5     | 300.0   | 10      | 7 <sub>HEX</sub> | Н                |

|                 | medium noise level    | 100 µV                    | 1 nA    | 1x10^5     | 100.0   | 10      | 6 <sub>HEX</sub> | Н                |

|                 | dynamic reserve 35 dB | 300 µV                    | 3 nA    | 3x10^4     | 30.0    | 10      | 5 <sub>HEX</sub> | Н                |

|                 | DC-drift 50 ppm/K     | 1 mV                      | 10 nA   | 1x10^4     | 10.0    | 10      | 4 <sub>HEX</sub> | Н                |

|                 |                       | 3 mV                      | 30 nA   | 3x10^3     | 3.0     | 10      | 3 <sub>HEX</sub> | Н                |

|                 |                       | 10 mV                     | 100 nA  | 1x10^3     | 1.0     | 10      | 2 <sub>HEX</sub> | Н                |

|                 |                       | 30 mV                     | 300 nA  | 3x10^2     | 0.3     | 10      | 1 <sub>HEX</sub> | Н                |

|                 |                       | 100 mV                    | 1 µA    | 1x10^2     | 0.1     | 10      | 0 <sub>HEX</sub> | Н                |

|                 |                       | 30 µV                     | 300 pA  | 3x10^5     | 300.0   | 10      | F <sub>HEX</sub> | L                |

|                 |                       | 100 µV                    | 1 nA    | 1x10^5     | 100.0   | 10      | E <sub>HEX</sub> | L                |

|                 |                       | 300 µV                    | 3 nA    | 3x10^4     | 30.0    | 10      | D <sub>HEX</sub> | L                |

|                 |                       | 1 mV                      | 10 nA   | 1x10^4     | 10.0    | 10      | C <sub>HEX</sub> | L                |

|                 |                       | 3 mV                      | 30 nA   | 3x10^3     | 3.0     | 10      | B <sub>HEX</sub> | L                |

|                 |                       | 10 mV                     | 100 nA  | 1x10^3     | 1.0     | 10      | A <sub>HEX</sub> | L                |

|                 |                       | 30 mV                     | 300 nA  | 3x10^2     | 0.3     | 10      | 9 <sub>HEX</sub> | L                |

|                 |                       | 100 mV                    | 1 µA    | 1x10^2     | 0.1     | 10      | 8 <sub>HEX</sub> | L                |

| Ultra-Stable    | high signal           | 300 µV                    | 3 nA    | 3x10^4     | 300.0   | 1       | 7 <sub>HEX</sub> | L                |

|                 | small noise level     | 1 mV                      | 10 nA   | 1x10^4     | 100.0   | 1       | 6 <sub>HEX</sub> | L                |

|                 | dynamic reserve 15 dB | 3 mV                      | 30 nA   | 3x10^3     | 30.0    | 1       | 5 <sub>HEX</sub> | L                |

|                 | DC-drift 5 ppm/K      | 10 mV                     | 100 nA  | 1x10^3     | 10.0    | 1       | 4 <sub>HEX</sub> | L                |

|                 |                       | 30 mV                     | 300 nA  | 3x10^2     | 3.0     | 1       | 3 <sub>HEX</sub> | L                |

|                 |                       | 100 mV                    | 1 µA    | 1x10^2     | 1.0     | 1       | 2 <sub>HEX</sub> | L                |

|                 |                       | 300 mV                    | 3 μΑ    | 3x10^1     | 0.3     | 1       | 1 <sub>HEX</sub> | L                |

|                 |                       | 1 V                       | 10 µA   | 1x10^1     | 0.1     | 1       | 0 <sub>HEX</sub> | L                |

Table 1: Gain and Dynamics LIA-MV(D)-200

#### 7.3 Adjusting the Phase

The correct phase adjustment between the input signal at very important in order to obtain maximum output signals

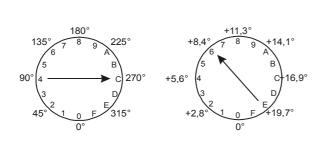

The phase can be adjusted with the hexadecimal-code sv<sup>"</sup>Y输出"将达到接近零件 "Fine" to achieve a maximum output signal at the "X-OUT 则双相模型的" ROUTPUT models LIA-MV**D**-200 the "Y-OUTPUT" will reach a value and Y are phase shifted by 90°. If the input signal has a si OUTPUT" of dual phase models automatically delivers the without the need for phase adjustment. If the signal is not 总共256步的调整。开关 QUTPUT" will show a phase dependence which might be filtering. Please contact FEMTO for details.

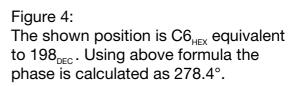

The phase is adjustable with the two hex-code switches in a total of 256 steps. The positions of the switches are encoded as an 8-bit word from 0 to 255, corresponding to  $00_{Hex}$ ...FF<sub>Hex</sub>, respectively.

Depending on the configuration of the lock-in amplifier and the chosen operating mode the phase shifter provides either 8 or 7 bit resolution (for standard configuration see chapter 5).

#### 7.3.1 Phase Shifter Resolution of 8 Bit

The code-switches "Coarse" and "Fine" enable 22.5° and 1.4° resolu respectively.

The 8 bit resolution is available for the following models and modes of

- L-models with standard configuration in 1f-mode.

- H-models with modified configuration for a maximum working 60 kHz in 1f-mode (for changing the standard configuration ple chapter 9).

If the phase shifter is set to 8 bit resolution the phase can be calculated as follows:

CODEDEC

256

Phase = 360

In a less mathematical way the code-switch "Coarse" represents directly the geometrical angle of the phase whereas the code switch "Fine" is used for the fine calibration.

-5°

8位分别

模式:

和1.4

大工作频率为60 kHz

率,则可以如下计算相位:

率可用于

标准配置,请参见第9章)。 如果将移相器设置为8位分辨

置的H型在1f

型号和操

`樟式下的

#### 7.3.2 Phase Shifter Resolution of 7 Bit

In this mode the code-switches "Coarse" and "Fine" enable 45° and 2.8 ° resolution, respectively.

The 7 bit resolution is available for the following models and operating modes:

- L-models with standard configuration in 2f-mode.

- H-models with standard configuration.

- H-models with modified configuration for a maximum working frequency of 60 kHz in 2f-mode (for changing the standard configuration please see chapter 9).

If the phase shifter is set to 7 bit resolution the phase can be calculated as follows:

$$Phase = 360 \cdot \frac{CODE_{DEC}}{128}$$

In a less mathematical way the geometrical angle of the code-switch "Coarse" represents half of the adjusted phase angle ( $45^{\circ}$  geometrical angle =  $90^{\circ}$  phase angle) whereas the code-switch "Fine" is used for the fine calibration.

Table 2 shows a few examples of different phase shifter settings and corresponding phase values.

| Code              |                   | Phase |       | Co                | de |

|-------------------|-------------------|-------|-------|-------------------|----|

| HEX               | DEC               | 8 bit | 7 bit | HEX               | DE |

| 00 <sub>HEX</sub> | 0 <sub>DEC</sub>  | 0°    | 0°    | 80 <sub>HEX</sub> | 12 |

| 20 <sub>HEX</sub> | 32 <sub>DEC</sub> | 45°   | 90°   | 08 <sub>HEX</sub> |    |

| 40 <sub>HEX</sub> | 64 <sub>DEC</sub> | 90°   | 180°  | $0C_{\text{HEX}}$ | 1  |

| 60 <sub>HEX</sub> | 96 <sub>DEC</sub> | 135°  | 270°  | E0 <sub>HEX</sub> | 22 |

| Code              |                    | Phase   |        |  |

|-------------------|--------------------|---------|--------|--|

| HEX               | DEC                | 8 bit   | 7 bit  |  |

| 80 <sub>HEX</sub> | 128 <sub>DEC</sub> | 180.00° | 360.0° |  |

| 08 <sub>HEX</sub> | 8 <sub>DEC</sub>   | 11.25°  | 22.5°  |  |

| 0C <sub>HEX</sub> | 12 <sub>DEC</sub>  | 16.90°  | 33.8°  |  |

| E0 <sub>HEX</sub> | 224 <sub>DEC</sub> | 315.00° | 630.0° |  |

Table 2: Examples of phase settings (8 bit and 7 bit resolution)

#### 7.4 2f-Mode

The LIA-MV(D)-200 Series Lock-In Amplifiers allow for the use of the 2f-mode.

In 2f-mode the lock-in amplifier detects the signal components at the second harmonic of the reference frequency. This mode is useful for measuring the harmonic content of a signal e.g. in resonance absorption measurements. When the 2f-mode is selected with DIP switch S2 the reference frequency will be internally doubled and the resolution of the phase shifter will be reduced to 7 bit (see chapter 7.3.2).

**Attention:** In standard configuration 2f-mode is only available for L-models. To use this mode with H-models a modified configuration is necessary (see chapter 9 for details).

#### 7.5 Time Constant and Filter Characteristics

The choice of the time constant is always a compromise between noise suppression and measurement time.

Increasing the time constant will result in a more accurate and less noisy output signal of the lock-in amplifier. At the same time the measurement period will increase as well as it takes more time to reach a stable output signal. The amount of fluctuations on the output signal is inverse proportional to the chosen time constant.

The measurement period is proportional to the time constant. As a rule of thumb it is advised to wait ca. five times the set time constant before reading the lock-in output in order to achieve an accurate and stable output signal. The accuracy is dependent on the measurement period and can be described by the following formula:

```

Error in %: \delta = 100 \text{ x} \exp(-t/\tau) t = measurement time,

\tau = \text{lock-in time-constant}

```

Example: If you chose a time constant of 1 s with the hexadecimal switch on the front panel you should wait ca. 5 s before reading the signal at the output of the lock-in. During this time the output signal will approach its final end-value. After 1 s the lock-in output will have reached 63 % of the end-value and the remaining error is 37%. After 2 s the error is 14 % and after 3 s only 5 %. After 5 s the lock-in output will have an error of less than 1 % with respect to the final end-value you would achieve after an infinite measurement period.

For setting the time-constant a low pass filter with either a 12 dB/octave or a 6 dB/octave characteristic can be chosen. Usually the 12 dB/octave characteristic should be used because of the much better noise performance. Only in closed-loop systems where stability is very important and may be negatively influenced by the second order filter the 6 dB/octave characteristic is more useful.

The time constant of the output low pass filter is selected by the hexadecimal switch "Time Constant".

| Time constant | Time constant | Hexadecir        | nal switch       |

|---------------|---------------|------------------|------------------|

| Model "-L"    | Model "-H"    | 6dB/Octave       | 12dB/Octave      |

| 3 ms          | 300 µs        | 0 <sub>HEX</sub> | 8 <sub>HEX</sub> |

| 10 ms         | 1 ms          | 1 <sub>HEX</sub> | 9 <sub>HEX</sub> |

| 30 ms         | 3 ms          | 2 <sub>HEX</sub> | $A_{_{HEX}}$     |

| 100 ms        | 10 ms         | 3 <sub>HEX</sub> | B <sub>HEX</sub> |

| 300 ms        | 30 ms         | 4 <sub>HEX</sub> | C <sub>HEX</sub> |

| 1 s           | 100 ms        | 5 <sub>HEX</sub> | D <sub>HEX</sub> |

| 3 s           | 300 ms        | 6 <sub>HEX</sub> | E <sub>HEX</sub> |

| 10 s          | 1 s           | 7 <sub>нех</sub> | F <sub>HEX</sub> |

| Table 3: Time constant | s |

|------------------------|---|

|------------------------|---|

F Ε Ο

#### 7.6 DIP Switches S1-S4

The 4 DIP switches shown in figure 2 control the following operating parameters:

| DIP switch S1  | Choice of high or low dynamic reserve. In combination with the "Sensitivity" hexadecimal switch the 3 modes of operation for the AC- and DC-amplifiers can be selected (see chapter 7.2)                                                                                                                                                                                                                                                                                                                  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP switch S2  | Enables either detection of the fundamental signal when<br>switched to "off" (1f-mode) or detection of the second harmonic<br>signal when switched to "on" (2f-mode).<br>When using H-models in the standard configuration S2 is<br>inoperative. To use 2f-mode with a H-model the internal jumper<br>settings need to be changed (see chapter 9.4). Please note that<br>the input fundamental signal as well as the maximum reference<br>frequency is limited to 60 kHz (see chapter 7.3.2, 7.4 and 9.4) |

| DIP switch S3  | Determines the time the internal PLL (Phase-Locked-Loop) circuit requires to lock to the external reference signal. The two settings are:                                                                                                                                                                                                                                                                                                                                                                 |

|                | SLOW: ("ON") This is the most common setting which<br>should be preferred if the measuring frequency is at a fix value.<br>The phase is extraordinary stable in this setting.                                                                                                                                                                                                                                                                                                                             |

|                | FAST: ("OFF") In frequency-sweeping measurements with an external oscillator sweeping relatively fast over a wide range (e.g. 100 Hz 10 kHz) best results are achieved with this setting.                                                                                                                                                                                                                                                                                                                 |

|                | If the unlocked LED is "ON" the PLL is not locked. In this case<br>make sure that the frequency and amplitude of your reference<br>signal are within the specified ranges. For reference frequencies<br>below 40 Hz we recommend the "slow" setting.                                                                                                                                                                                                                                                      |

| DIP Switch S4: | Selects the threshold level for the reference comparator.<br>For e.g. a sinusoidal reference signal centered around zero with<br>a voltage of $\pm 100$ mV $\pm 5$ V or analog reference signals without<br>DC-shift the level should be set to "0 V".                                                                                                                                                                                                                                                    |

If the reference signal is a digital signal (TTL, CMOS) the switch should be set to "2 V".

| Dip switch | Switch setting                       |                                      |  |  |

|------------|--------------------------------------|--------------------------------------|--|--|

|            | OFF                                  | ON                                   |  |  |

| S1         | Low Drift and High<br>Dynamic Mode   | Ultra-Stable and Low<br>Drift Mode   |  |  |

| S2         | 1f-Mode                              | 2f-Mode                              |  |  |

| S3         | PLL Fast Locking                     | PLL Slow Locking                     |  |  |

| S4         | Threshold of<br>Reference Input =0 V | Threshold of<br>Reference Input =2 V |  |  |

Table 4: DIP Switches

# **F E 🏊 T O**°

### 8 Operation with Control Interface

The LIA-MV(D)-200 Series Lock-In Amplifiers provide TTL/CMOS-compatible digital inputs which are isolated from the analog circuits by opto-couplers. The digital input levels must remain static during a measurement. The best choice for providing the TTL-bits and programming the lock-in amplifier is a standard PC I/O interface card with digital outputs. A high-level at the TTL-input presents a logical 1.

The digital inputs of the lock-in consist of 3 groups. The first group controls the phase shift. These 8 bits correspond, as described in chapter 7.3, to a binary number of 0 to 255. A second group of four bits controls the time constants and a third group of four bits manages the full scale sensitivity of the lock-in amplifier. Finally, there is one further digital input which can be used to disable the local hexadecimal switches on the front panel (see chapter 8.3).

The DIP switches cannot be remote controlled.

#### 8.1 Assignment of the SUB-D 25 Pin Socket

| Pin 1<br>Pin 2:  | +12 V (Stabilized Power Supply Output)<br>-12 V (Stabilized Power Supply Output) |

|------------------|----------------------------------------------------------------------------------|

| Pin 2:<br>Pin 3: | AGND (Analog Ground)                                                             |

| Pin 4:           | +5 V (Stabilized Power Supply Output)                                            |

| Pin 5:           | X-Output                                                                         |

| Pin 6:           | Overload Status Output                                                           |

| Pin 7:           | Unlocked Status Output                                                           |

| Pin 8:           | Disable Local Switch Control Input                                               |

| Pin 9:           | DGND (Ground for Digital Control Pins 8 - 25)                                    |

| Pin 10:          | Dynamic Mode (DYN0)                                                              |

| Pin 11:          | Sensitivity (SEN0)                                                               |

| Pin 12:          | Sensitivity (SEN1)                                                               |

| Pin 13:          | Sensitivity (SEN2)                                                               |

| Pin 14:          | Time Constant Slope (TCSL)                                                       |

| Pin 15:          | Time Constant (TC0)                                                              |

| Pin 16:          | Time Constant (TC1)                                                              |

| Pin 17:          | Time Constant (TC2)                                                              |

| Pin 18:          | Phase Shift (PH0)                                                                |

| Pin 19:          | Phase Shift (PH1)                                                                |

| Pin 20:          | Phase Shift (PH2)                                                                |

| Pin 21:          | Phase Shift (PH3)                                                                |

| Pin 22:          | Phase Shift (PH4)                                                                |

| Pin 23:          | Phase Shift (PH5)                                                                |

| Pin 24:          | Phase Shift (PH6)                                                                |

| Pin 25:          | Phase Shift (PH7)                                                                |

| Time ( | Constants                   |                             | 6/12 dB<br>Octave        | T.C.<br>MSB | T.C.   | T.C.<br>LSB |        |

|--------|-----------------------------|-----------------------------|--------------------------|-------------|--------|-------------|--------|

| HEX    | Time constant<br>Model "-L" | Time constant<br>Model "-H" | Filter<br>characteristic | Pin 14      | Pin 17 | Pin 16      | Pin 15 |

| 0      | 3 ms                        | 300 µs                      | 6 dB                     | Low         | Low    | Low         | Low    |

| 1      | 10 ms                       | 1 ms                        | 6 dB                     | Low         | Low    | Low         | High   |

| 2      | 30 ms                       | 3 ms                        | 6 dB                     | Low         | Low    | High        | Low    |

| 3      | 100 ms                      | 10 ms                       | 6 dB                     | Low         | Low    | High        | High   |

| 4      | 300 ms                      | 30 ms                       | 6 dB                     | Low         | High   | Low         | Low    |

| 5      | 1 s                         | 100 ms                      | 6 dB                     | Low         | High   | Low         | High   |

| 6      | 3 s                         | 300 ms                      | 6 dB                     | Low         | High   | High        | Low    |

| 7      | 10 s                        | 1 s                         | 6 dB                     | Low         | High   | High        | High   |

| 8      | 3 ms                        | 300 µs                      | 12 dB                    | High        | Low    | Low         | Low    |

| 9      | 10 ms                       | 1 ms                        | 12 dB                    | High        | Low    | Low         | High   |

| Α      | 30 ms                       | 3 ms                        | 12 dB                    | High        | Low    | High        | Low    |

| В      | 100 ms                      | 10 ms                       | 12 dB                    | High        | Low    | High        | High   |

| С      | 300 ms                      | 30 ms                       | 12 dB                    | High        | High   | Low         | Low    |

| D      | 1 s                         | 100 ms                      | 12 dB                    | High        | High   | Low         | High   |

| E      | 3 s                         | 300 ms                      | 12 dB                    | High        | High   | High        | Low    |

| F      | 10 s                        | 1 s                         | 12 dB                    | High        | High   | High        | High   |

# 8.2 Overview of all Digitally Controllable Functions

Table 5: Time Constants

| Full-Scale Sensitivity<br>at DIP switch S1 = OFF |                  |           | Low Drift<br>High Dyn. | Sensitiv.<br>MSB | Sensitiv. | Sensitiv.<br>LSB |        |

|--------------------------------------------------|------------------|-----------|------------------------|------------------|-----------|------------------|--------|

| HEX                                              | Voltage<br>Input | Low Drift | High<br>Dyn.           | Pin 10           | Pin 13    | Pin 12           | Pin 11 |

| 0                                                | 100 mV           | Х         | -                      | Low              | Low       | Low              | Low    |

| 1                                                | 30 mV            | Х         | -                      | Low              | Low       | Low              | High   |

| 2                                                | 10 mV            | Х         | -                      | Low              | Low       | High             | Low    |

| 3                                                | 3 mV             | Х         | -                      | Low              | Low       | High             | High   |

| 4                                                | 1 mV             | Х         | -                      | Low              | High      | Low              | Low    |

| 5                                                | 300 µV           | Х         | -                      | Low              | High      | Low              | High   |

| 6                                                | 100 µV           | Х         | -                      | Low              | High      | High             | Low    |

| 7                                                | 30 µV            | Х         | -                      | Low              | High      | High             | High   |

| 8                                                | 10 mV            | -         | Х                      | High             | Low       | Low              | Low    |

| 9                                                | 3 mV             | -         | Х                      | High             | Low       | Low              | High   |

| А                                                | 1 mV             | -         | Х                      | High             | Low       | High             | Low    |

| В                                                | 300 µV           | -         | Х                      | High             | Low       | High             | High   |

| С                                                | 100 µV           | -         | Х                      | High             | High      | Low              | Low    |

| D                                                | 30 µV            | -         | Х                      | High             | High      | Low              | High   |

| E                                                | 10 µV            | -         | Х                      | High             | High      | High             | Low    |

| F                                                | 3 μV             | -         | Х                      | High             | High      | High             | High   |

**Τ** Ο <sup>®</sup>

F E

| Full-Scale Sensitivity<br>at DIP switch S1 = ON |                  |                  | Ultra-Stab.<br>Low Drift. | Sensitiv.<br>MSB | Sensitiv. | Sensitiv.<br>LSB |        |

|-------------------------------------------------|------------------|------------------|---------------------------|------------------|-----------|------------------|--------|

| HEX                                             | Voltage<br>Input | Ultra-<br>Stable | Low Drift                 | Pin 10           | Pin 13    | Pin 12           | Pin 11 |

| 0                                               | 1 V              | Х                | -                         | Low              | Low       | Low              | Low    |

| 1                                               | 300 mV           | Х                | -                         | Low              | Low       | Low              | High   |

| 2                                               | 100 mV           | Х                | -                         | Low              | Low       | High             | Low    |

| 3                                               | 30 mV            | Х                | -                         | Low              | Low       | High             | High   |

| 4                                               | 10 mV            | Х                | -                         | Low              | High      | Low              | Low    |

| 5                                               | 3 mV             | Х                | -                         | Low              | High      | Low              | High   |

| 6                                               | 1 mV             | Х                | -                         | Low              | High      | High             | Low    |

| 7                                               | 300 µV           | Х                | -                         | Low              | High      | High             | High   |

| 8                                               | 100 mV           | -                | Х                         | High             | Low       | Low              | Low    |

| 9                                               | 30 mV            | -                | Х                         | High             | Low       | Low              | High   |

| Α                                               | 10 mV            | -                | Х                         | High             | Low       | High             | Low    |

| В                                               | 3 mV             | -                | Х                         | High             | Low       | High             | High   |

| С                                               | 1 mV             | -                | Х                         | High             | High      | Low              | Low    |

| D                                               | 300 µV           | -                | Х                         | High             | High      | Low              | High   |

| E                                               | 100 µV           | -                | Х                         | High             | High      | High             | Low    |

| F                                               | 30 µV            | -                | Х                         | High             | High      | High             | High   |

Table 6: Sensitivity

| Phase Coarse |       | Phase<br>(Ph 7) | Phase<br>(Ph 6) | Phase<br>(Ph 5) | Phase<br>(Ph 4) |        |

|--------------|-------|-----------------|-----------------|-----------------|-----------------|--------|

| HEX          | Deg   | ree             |                 | SUB- D 2        | 5 Socket        |        |

|              | 8 Bit | 7 Bit           | Pin 25          | Pin 24          | Pin 23          | Pin 22 |

| 0            | 0.0   | 0               | Low             | Low             | Low             | Low    |

| 1            | 22.5  | 45              | Low             | Low             | Low             | High   |

| 2            | 45.0  | 90              | Low             | Low             | High            | Low    |

| 3            | 67.5  | 135             | Low             | Low             | High            | High   |

| 4            | 90.0  | 180             | Low             | High            | Low             | Low    |

| 5            | 112.5 | 225             | Low             | High            | Low             | High   |

| 6            | 135.0 | 270             | Low             | High            | High            | Low    |

| 7            | 157.5 | 315             | Low             | High            | High            | High   |

| 8            | 180.0 | 360             | High            | Low             | Low             | Low    |

| 9            | 202.5 | 405             | High            | Low             | Low             | High   |

| А            | 225.0 | 450             | High            | Low             | High            | Low    |

| В            | 247.5 | 495             | High            | Low             | High            | High   |

| С            | 270.0 | 540             | High            | High            | Low             | Low    |

| D            | 292.5 | 585             | High            | High            | Low             | High   |

| Е            | 315.0 | 630             | High            | High            | High            | Low    |

| F            | 337.5 | 675             | High            | High            | High            | High   |

F E T O

| Phase Fine |       |       | Phase<br>(Ph 3) | Phase<br>(Ph 2) | Phase<br>(Ph 1) | Phase<br>(Ph 0) |

|------------|-------|-------|-----------------|-----------------|-----------------|-----------------|

| HEX        | Deg   | jree  |                 | SUB- D 2        | 5 Socket        |                 |

|            | 8 Bit | 7 Bit | Pin 21          | Pin 20          | Pin 19          | Pin 18          |

| 0          | 0.00  | 0.00  | Low             | Low             | Low             | Low             |

| 1          | 1.41  | 2.81  | Low             | Low             | Low             | High            |

| 2          | 2.81  | 5.62  | Low             | Low             | High            | Low             |

| 3          | 4.22  | 8.44  | Low             | Low             | High            | High            |

| 4          | 5.63  | 11.25 | Low             | High            | Low             | Low             |

| 5          | 7.03  | 14.10 | Low             | High            | Low             | High            |

| 6          | 8.44  | 16.90 | Low             | High            | High            | Low             |

| 7          | 9.84  | 19.70 | Low             | High            | High            | High            |

| 8          | 11.25 | 22.50 | High            | Low             | Low             | Low             |

| 9          | 12.70 | 25.40 | High            | Low             | Low             | High            |

| Α          | 14.10 | 28.20 | High            | Low             | High            | Low             |

| В          | 15.50 | 31.00 | High            | Low             | High            | High            |

| С          | 16.90 | 33.80 | High            | High            | Low             | Low             |

| D          | 18.30 | 36.60 | High            | High            | Low             | High            |

| Е          | 19.70 | 39.40 | High            | High            | High            | Low             |

| F          | 21.10 | 42.20 | High            | High            | High            | High            |

Table 7: Phase Shifter: 8 bit and 7 bit Resolution

#### 9 Mixed Operation

F

There are two ways of remote control operation depending on the digital signal at the input "Disable Local Switch Control" (Pin 8 of SUB-D 25 socket). High-level applied to this input enables exclusive remote control operation of the settings for time-constant, sensitivity and phase. All manual hexadecimal switches are out of function in this mode. Only the DIP switch settings are relevant as these cannot be remotely controlled.

A mixed mode of operation with digitally remote and manually controlled functions is enabled when Pin 8 is left open or set to "Low". The internal and external controlbits are then connected by a logical OR function. To ensure a perfect remote control operation in this mixed mode make sure to switch the corresponding hexadecimalswitches to position "0". The other remaining switches allow for manual operation.

#### 10 Advanced Configuration of the Lock-In Amplifier

Attention: The following advanced configuration requires opening the housing of the lock-in amplifier. Read the documentation carefully before opening the device. Close the device before putting it back into operation. When changing the configuration pay close attention to the instructions provided further down. A failure in the configuration can damage the device and may expose you to shocks and other hazards.

#### 10.1 Opening and Closing the Device

Before opening the device remove the power supply cable and all signal lines. Remove the 2 upper screws from the rear panel and the 2 upper screws from the front panel. You may also slightly loosen the 2 lower screws on the front panel allowing the top lid to open up smoothly.

Attention: On older models a grounding wire attached to the main board is fixed by the upper left screw on the rear panel. When loosening the screw a toothed lock washer may fall down on the board of the lock-in amplifier. Remove the toothed lock washer to avoid damage (or short circuit) to the board. On newer models the ground wire is attached by a flat connection directly to the top lid. You can leave this connector plugged while changing the configuration of the lock-in amplifier.

After changing the configuration close the housing by starting with the left upper screw of the rear panel. Insert the toothed lock washer between the case and the rear panel together with the feeder clamp of the grounding wire before mounting the screw. On newer models with a direct grounding connection to the top lid you can mount the left upper screw right away without the need of attaching a washer or feeder clamp first. After fastening the left upper screw mount the right upper screw of the rear panel and the remaining 4 screws of the front panel.

Please bear in mind that the housing is made of relatively soft aluminum. Therefore pay attention when tightening the screws as too much torque may damage the tapped holes.

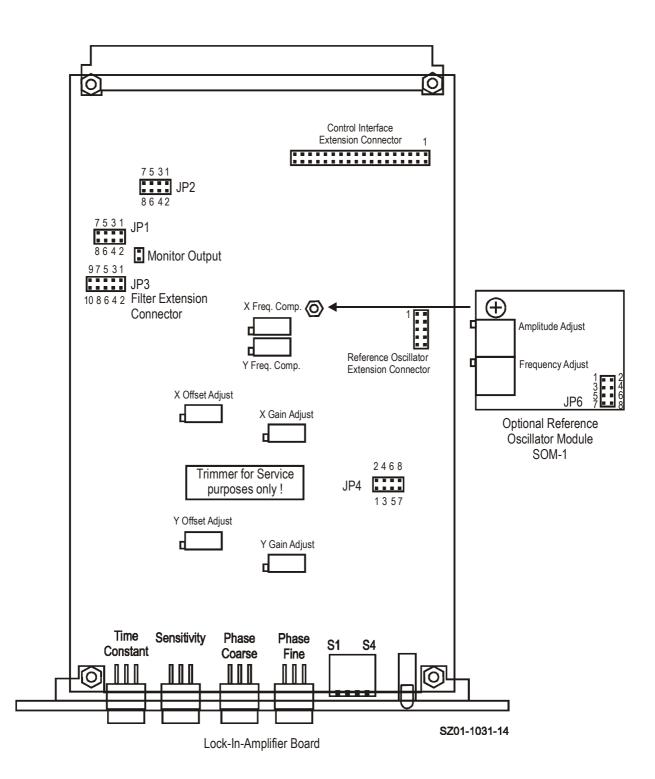

#### 10.2 Optional Sine-Oscillator-Module SOM-1

The optional Sine-Oscillator-Module SOM-1 is especially designed for those applications where a fixed reference frequency is required and an external reference generator is not available to modulate the signal source and drive the reference frequency input of the lock-in amplifier.

The SOM-1 can be set to generate a reference frequency between 5 Hz and 130 kHz without an additional signal generator. The reference frequency and amplitude of the module are adjustable by a trimpot and a jumper setting (see figure 5). The SOM-1 is optimized for fixed frequency operation. Therefore in applications where the reference frequency has to be varied during the measurement within the specified range of the LIA-MV(D)-200 an external reference oscillator should be used.

The SOM-1 requires a supply voltage of  $\pm 15$  V which is supplied by the lock-in amplifier. It is delivered in standard configuration with the following pre-settings:

Frequency: 1.0 kHz

Amplitude: 1 V<sub>ms</sub>.

To modify these settings you have to open the device (see chapter 9.1).

First, the user has to decide which reference frequency is adequate for his application. The reference frequency has to be within the specified range of the LIA-MV(D)-200 module. There are 4 ranges for the reference frequency which can be selected by the jumper JP6 on the SOM-1 module (see datasheet of the SOM-1 module for details). The trimpot "frequency adjust" adjusts the frequency within these ranges. The trimpot "amplitude adjust" allows to adjust the amplitude, which can be set from 0 to 2 V<sub>rms</sub>. The maximum output current of the oscillator is  $\pm 5$  mA.

Routing the SOM-1 frequency to the BNC socket (labeled "Reference Input") requires the setting of the relevant jumpers in the jumper field 3 on the adapterboard of the lock-in amplifier (see table 10 and figure 6). Once the jumpers are set correctly the frequency and amplitude can be checked at the BNC socket labeled "REFERENCE INPUT".

The SOM-1 needs a relatively long warm-up time of up to 30 minutes after switching on the power supply. During this warm-up time the frequency can drift up to 15 %. If a more stable frequency is needed an external reference frequency should be used for synchronization (see table 10).

When the operation mode with synchronization to an externally supplied reference frequency is used, the free running frequency of the SOM-1 module must be adjusted approximately to the reference frequency before connecting the reference signal to the REF.INPUT socket. This ensures that the PLL on the SOM-1 module locks to the fundamental of the reference signal rather than a harmonic.

For further information please see also the datasheet of the SOM-1 module!

#### 10.3 Modification of the Input Signal Filters

The LIA-MV(D)-200 series provides adjustable input signal filters. Optimizing the filter settings can increase the dynamic reserve which might be important especially for measurements in noisy environments. The lower and upper cut-off frequency can be set independently by a low pass and a high pass filter according to the following table (see figure 5 for the jumper positions):

| lower cut-off frequency (-3dB)<br>Model -L Model -H |        | JP3   | upper cut-off<br>frequency (-3dB) | JP1   | JP2   |

|-----------------------------------------------------|--------|-------|-----------------------------------|-------|-------|

| 0.2 Hz*                                             | 2 Hz*  | 3 – 4 | 100 Hz                            | 1 – 2 | 1 – 2 |

| 1.0 Hz                                              | 10 Hz  | 1 – 3 | 1 kHz                             | 3 – 4 | 3 – 4 |

| 10.0 Hz                                             | 100 Hz | 2 – 4 | 10 kHz                            | 5 – 6 | 5 – 6 |

| 100.0 Hz                                            | 1 kHz  | 3 – 5 | 100 kHz                           | 7 – 8 | 7 – 8 |

| 1.0 kHz                                             | 10 kHz | 4 – 6 | > 1 MHz*                          | free  | free  |

\* standard configuration

Table 8: Setting of the Signal Filters: Jumpers JP1-JP3

#### **10.4 Setting the Working Frequency Range (H-Models Only)**

The factory setting for the H-model lock-in amplifiers provides a working frequency range from 50 Hz to 120 kHz with a phase shifter resolution of 7 bit. The switch "S2" for selecting the 2f-mode is inoperative. If you need 2f-mode or a phase shifter resolution of 8 bit you have to change the jumpers in field 4 (see table 9). Please note that this will limit the working frequency to a range of 50 Hz to ca. 60 kHz.

| Model | Frequencies at<br>Reference input       | Lock-In<br>Mode | Jumper<br>Block<br>JP4 | Position<br>DIP switch<br>S2 | Phase<br>Shifter<br>Resolution |

|-------|-----------------------------------------|-----------------|------------------------|------------------------------|--------------------------------|

| -L    | 5 Hz ≤ f ≤ 10kHz                        | 1f              | 1 – 2                  | 1f                           | 8 bit                          |

| -L    | 5 Hz ≤ f ≤ 10kHz                        | 2f              | 1 – 2                  | 2f                           | 7 bit                          |

| -H    | 50 Hz ≤ f ≤ 120kHz<br>(factory setting) | 1f              | 3 – 4<br>and<br>5 – 6  | irrelevant                   | 7 bit                          |

| -H    | 50 Hz ≤ f ≤ 60kHz                       | 1f              | 1 – 2                  | 1f                           | 8 bit                          |

| -H    | 50 Hz ≤ f ≤ 60kHz                       | 2f              | 1 – 2                  | 2f                           | 7 bit                          |

Table 9:Jumper Settings for Different Working Frequency Ranges and<br/>Operating Modes

Figure 5: Overview of the Jumper Positions

TO®

F

Ε

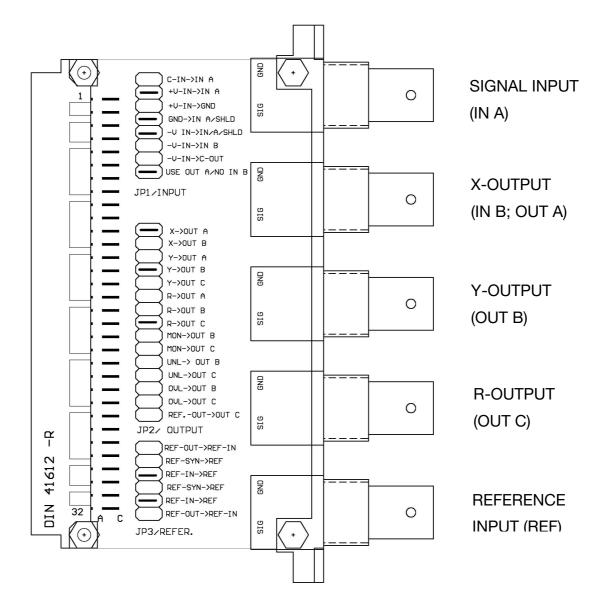

#### 10.5 Changing the Assignment of the BNC Sockets

The assignment of the BNC sockets on the rear panel can be changed and adapted to the particular operation conditions.

Figure 6: View of the Jumper Field of the Adapter Board for a Dual Phase Model LIA-MVD-200 Showing Standard Configuration without SOM-1 Sine Oscillator Module.

Remark: Single phase models LIA-MV-200 do not contain the BNC sockets "Y-OUTPUT" and "R-OUTPUT".

The following options for special configurations correspond mostly to dual phase models LIA-MVD-200.

#### 10.5.1 Options for the Assignment of the BNC Socket "REFERENCE INPUT"

| Socket Function                                                                                                           | S       | et Jumper |    | Jumper Field |

|---------------------------------------------------------------------------------------------------------------------------|---------|-----------|----|--------------|

| An external reference frequency is<br>used.<br>(standard configuration without<br>SOM-1 module)                           | REF-IN  | ->REF     | 2x | JP3          |

| The signal of the SOM-1 module is                                                                                         | REF-OUT | ->REF-IN  | 2x | JP3          |

| used as internal reference frequency<br>and is externally available too.<br>(standard configuration with<br>SOM-1 module) | REF-IN  | ->REF     | 2x | JP3          |

| The signal of the SOM-1 module is                                                                                         | REF-SYN | -> REF    | 2x | JP3          |

| used as internal reference frequency<br>and can be synchronized with an                                                   | REF-OUT | -> OUT C  | 1x | JP2          |

| external signal generator.                                                                                                | REF-OUT | -> REF-IN | 2x | JP3          |

| The reference signal of the SOM-1 module is also externally available at the socket "R-OUTPUT".                           |         |           |    |              |

| (dual phase models only)                                                                                                  |         |           |    |              |

Table 10: Assignments of the BNC Socket "REFERENCE INPUT"

| Socket Function                                                                                                                                                                                                                                                       |       | Set Jumper   |    | Jumper Field |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|----|--------------|

| AC coupled voltage input, single                                                                                                                                                                                                                                      | +V-IN | -> IN A      | 1x | JP1          |

|                                                                                                                                                                                                                                                                       | GND   | -> IN A/SHLD | 1x | JP 1         |

| The socket "X OUTPUT" is used as output "OUT A"                                                                                                                                                                                                                       | –V-IN | -> IN A/SHLD | 1x | JP 1         |

| (standard configuration)                                                                                                                                                                                                                                              | USE O | UT A/NO IN B | 1x | JP 1         |

| AC coupled voltage input,                                                                                                                                                                                                                                             | +V-IN | -> IN A      | 1x | JP 1         |

| differential, 1x BNC                                                                                                                                                                                                                                                  | –V-IN | -> IN A/SHLD | 1x | JP 1         |

| The center conductor and the outer<br>conductor of the socket "SIGNAL<br>INPUT" are used as differential input.<br>The outer conductor is NOT internally                                                                                                              | USE O | UT A/NO IN B | 1x | JP 1         |

| connected to ground<br>The socket "X OUTPUT" is used as<br>output "OUT A"                                                                                                                                                                                             |       |              |    |              |

| AC coupled voltage input,                                                                                                                                                                                                                                             | +V-IN | -> IN A      | 1x | JP 1         |

| differential, 2x BNC                                                                                                                                                                                                                                                  | GND   | -> IN A/SHLD | 1x | JP 1         |

| The center conductors of the sockets<br>"SIGNAL INPUT" and "X-OUTPUT"                                                                                                                                                                                                 | –V-IN | -> IN B      | 1x | JP 1         |

| are used as symmetric signal input.<br>The outer conductors of the two<br>sockets are grounded.<br>The BNC socket "Y-OUTPUT" is<br>used as X-Output for dual phase<br>models. *<br>For single phase models PIN 5 of the<br>SUB-D 25 socket must be used as<br>output. | x     | -> OUT B     | 1x | JP 2         |

| Current input, asymmetric                                                                                                                                                                                                                                             | C-IN  | -> IN A      | 1x | JP 1         |

| (single ended)                                                                                                                                                                                                                                                        | GND   | -> IN A/SHLD | 1x | JP 1         |

| The socket "SIGNAL INPUT" is set<br>as current input with a                                                                                                                                                                                                           | –V-IN | -> C-OUT     | 1x | JP 1         |

| transimpedance gain of -100 kV/A                                                                                                                                                                                                                                      | +V-IN | -> GND       | 1x | JP 1         |